# Rapid Single Flux Quantum (RSFQ) – Design Rules

# for Nb/Al<sub>2</sub>O<sub>3</sub>-Al/Nb-Process at

# Leibniz IPHT

Version 10.03.2017: RSFQ1H-1.6

## Address: Leibniz Institute of Photonic Technology (IPHT)

Department of Quantum Detection P.O. Box 100 239 D - 07702 Jena Germany

**Contact:** Prof. Dr. H.-G. Meyer (Head of Department)

| phone:  | + 49 3641 206116                 |

|---------|----------------------------------|

| FAX:    | + 49 3641 206198                 |

| e-mail: | hans-georg.meyer(at)ipht-jena.de |

Dr. J. Kunert (RSFQ Design)

| phone:  | + 49 3641 206127               |

|---------|--------------------------------|

| FAX:    | + 49 3641 206199               |

| e-mail: | juergen.kunert(at)ipht-jena.de |

Internet: http://www.fluxonics-foundry.de

# RSFQ design rulesIPHT JenaVersion 1.6Nb/Al2O3-Al/Nb-technologyProcess: RSFQ1H

Date: 3/10/2017

## A. Photomasks:

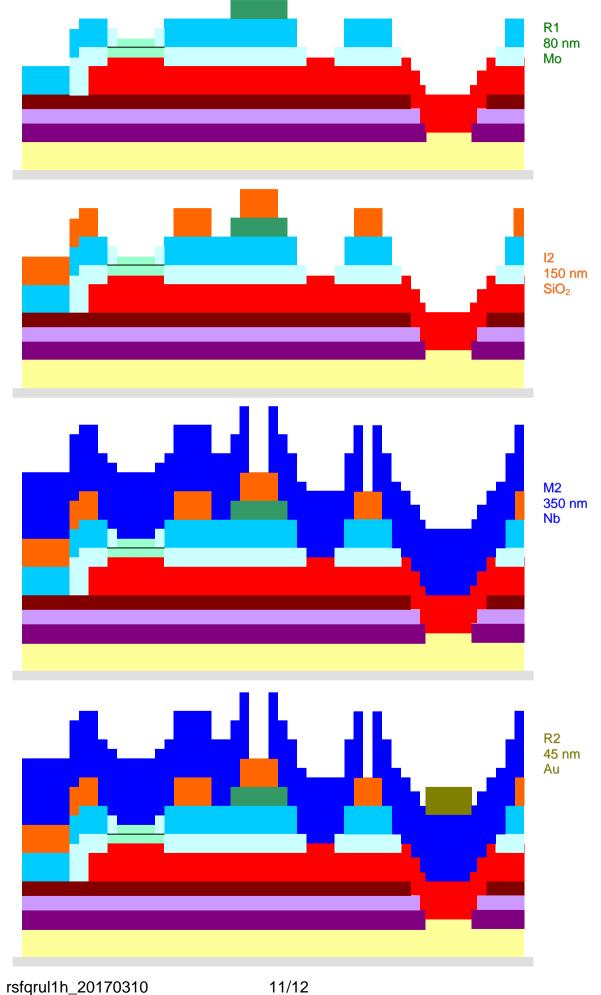

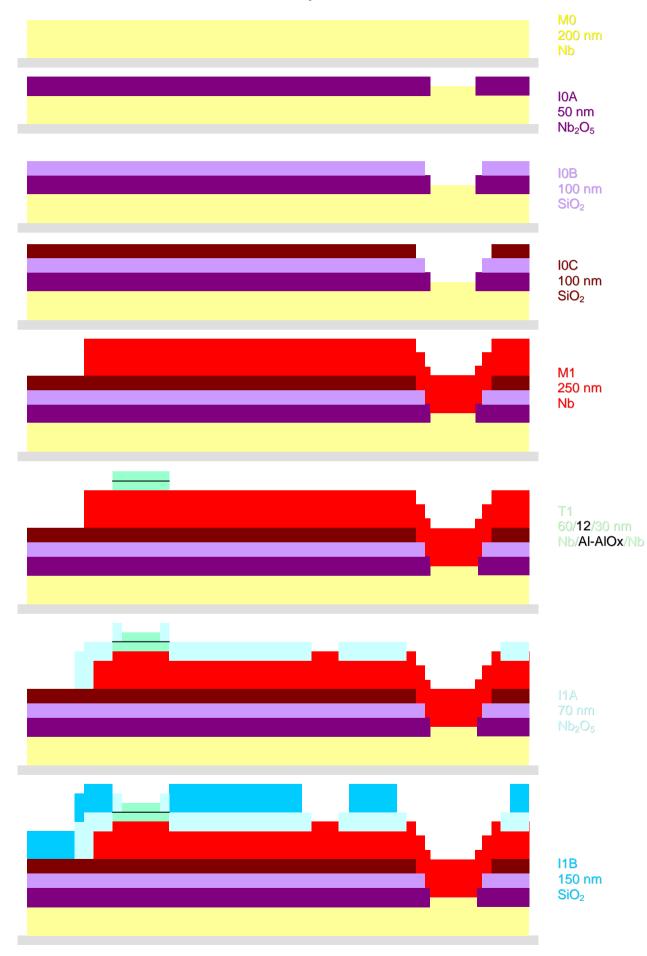

|   |     |     |          | Color       | Material                       | Thickness/ | Description            | Mask     | Wafer  | Process |

|---|-----|-----|----------|-------------|--------------------------------|------------|------------------------|----------|--------|---------|

|   | No. |     | polarity |             |                                | nm         |                        | polarity | resist |         |

| А | 1   | M0  | positive | Yellow      | Nb                             | 200        | Ground plane           | dark     | +      | etch    |

| В | 2   | I0A | negative | Violett     | Nb <sub>2</sub> O <sub>5</sub> | 50         | Holes in anodisation   | clear    | -      | anod    |

| С | 3   | I0B | negative | Magenta     | SiO <sub>2</sub>               | 100        | Holes in isolation     | clear    | +      | etch    |

| D | 4   | I0C | negative | Brown       | SiO <sub>2</sub>               | 100        | Holes in isolation     | clear    | +      | etch    |

| E | 5   | M1  | positive | Red         | Nb                             | 250        | Wiring1                | dark     | +      | etch    |

| F | 6   | T1  | positive | Light green | Nb/Al/Nb                       | 60/12/30   | Trilayer package       | clear    | -      | etch    |

| G | 7   | I1A | negative | Light blue  | Nb <sub>2</sub> O <sub>5</sub> | 70         | Holes in anodisation,  | clear    | -      | anod    |

|   |     |     |          |             |                                |            | Definition of junction |          |        |         |

| Н | 8   | CUT | positive | Light gray  |                                |            | Cutting of bridges for | clear    | +      | etch    |

|   |     |     |          |             |                                |            | anodisation            |          |        |         |

| I | 9   | I1B | negative | Cyan        | SiO <sub>2</sub>               | 150        | Holes in isolation     | clear    | +      | etch    |

| J | 10  | R1  | positive | Green       | Мо                             | 80         | Resistance layer       | dark     | -      | liftoff |

| K | 11  | 12  | negative | Coral       | SiO <sub>2</sub>               | 150        | Holes in isolation     | clear    | +      | etch    |

| L | 12  | M2  | positive | Blue        | Nb                             | 350        | Wiring 2               | dark     | +      | etch    |

| М | 13  | R2  | positive | Dark green  | Au                             | 45         | Bond pads, optional    | dark     | -      | liftoff |

| N | 14  | 13  | negative | Light brown | SiO                            | 400        | Holes in cover         | clear    | -      | liftoff |

Positive layout polarity means you design the physical structures as seen on the screen, negative means you design holes in the material. Clear mask polarity means that the mask is transparent wherever the patterns are drawn and dark means the opposite case.

## **B.** Auxiliary Layers:

| GDS II-No. | Name   | Layout polarity | Place on mask                 | Description                                                        |

|------------|--------|-----------------|-------------------------------|--------------------------------------------------------------------|

| 15         | SMA    | Positive        | all                           | Used for text and labels on masks                                  |

| 16         | SMC    | Positive        | N-13                          | Used for text and labels on chip                                   |

| 17         | MON    | Negativ         | A-M0                          | Defines holes (moats) in M0 plane by XOR with A-M0                 |

| 18         | TEXT   | Positive        | none                          | Used for help lines and notes                                      |

| 19         | TERM   |                 | none                          | Defines ports for L-meter inductance<br>calculation                |

| 20         | INVERT |                 | All with dark mas<br>polarity | skArea to invert polarity to use only masks<br>with polarity clear |

| 25         | M1N    |                 |                               | M1 xor M1N for Stepper Mask                                        |

| 22         | M2N    |                 |                               | M2 xor M2N for Stepper Mask                                        |

#### Remarks and auxiliary layers:

- Structures in layer SMA (GDS II-No. 15) are put on all masks.

- Holes in the M0 plane (moats) can be drawn on a separate layer M0N (GDS II-No. 17). For photo mask production this layer will be subtracted from layer M0 (GDS II-No. 1).

- TEXT layer (GDS II-No. 18) is used for additional text and other structures (lines, polygons etc.) during layout generation. It is **not put on masks**.

- To meet the correct value the holes in anodisation will be increased of 100nm by a resize operation during data preparation

#### C. Basic design rules:

- **1. Patterns** (for all layers)

- Data points on a grid smaller than 0.1 μm will be rounded to this 0.1 μm during compilation of the data.

#### 2. Width and spacing inside single layers

#### 2.1 Layers M0, M1, M2, M0N:

- Width  $\geq$  2.5 µm.

- Spacing  $\geq$  2.5 µm,

#### 2.2 Layer M2:

- Width W and spacing S of long interconnection lines between circuits and contact pads should be as large as the layout permits (standard value W = S, W = 100 μm).

- 2.3 Layer IOA, IOB, IOC, I1A, I1B, I2:

- Minimum contact hole size is  $3 \mu m \times 3 \mu m$ ,

- Spacing between different contact holes is  $\geq$  5 µm.

- Spacing Inside I0A,  $I1A \ge 5 \ \mu m$

#### 2.4 Layer I1A:

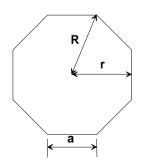

- Size of Josephson junction is defined by I1A. The JJs have an octagon form and the smallest JJ has an area of 12.5  $\mu$ m<sup>2</sup> with an inner diameter (see page 7) of the octagon of 3.8  $\mu$ m.

- 2.5 Layer CUT:

- For cutting wires in M0 or M1; these lines have to be longer than 15 μm, see section 6.

- 2.6 Layer T1:

- Spacing  $\geq 5 \ \mu m$ .

- T1 used only to form JJ. Size of JJ is defined by I1A.

#### 2.7 Layer R1:

- Width  $\geq$  5 µm.

- Spacing  $\geq 5 \ \mu m$ ,

- Widths of bias resistors are fixed to 10  $\mu$ m, spacing  $\geq$  5  $\mu$ m.

- Widths of shunt resistors should be not less than 10  $\mu$ m, spacing  $\geq$  5  $\mu$ m.

#### 2.8 Layer SMA:

• Text should be readable by eyes, recommended text high of 7 mm

#### 2.9 Layer SMC:

- Width  $\geq$  5 µm

- Text for description, owner and copyright

- Additional chip numbering is added during chip placement

#### 2.10 Layer I3:

- Cover the chip surface against mechanical influences

- Includes only holes for bond pads, for dicing frame and for structures defined by layer SMC

#### 3. Spacing between different layers

#### 3.1 All layers:

- Spacing between edges of structures in different layers is usually  $\geq$  2.5 µm.

- 3.2 Layers T1, I1B, and I2:

- Radius of octagonal area in T1 for JJs is 2.5 µm larger than the radius of window in isolation layer I1B. T1 and I2 coincide.

- 3.3 Layers T1 and M1:

- Distance to next edges below has to be  $\geq$  2.5 µm.

- 3.4 Layers I1A and I1B:

- Radius of octagonal contact holes in I1B for JJs is 2.5 µm larger than the radius of JJs (I1A).

- For vias: spacing between I1B and I1A is  $\geq$  2.5 µm.

- 3.5 Layers I1B and I2:

- Radius of octagonal contact holes in I2 for JJs is 2.5 µm larger than the radius of holes in I1B.

- For vias: spacing between I1B and I2 is  $\geq$  2.5 µm.

- 3.6 Layers I1A and I2:

- Edges of contact holes in I1A may coincide with I2, if smallest size in via is defined by I1B.

- 3.7 Layers CUT, IOA, IOB, IOC, and I1A:

- Below CUT edges of I0A, I0B, I0C and I1A may coincide.

- If CUT, I0A, I0B, I0C and I1A coincide, then CUT can cross structures in M0 or M1, but not both.

- Spacing Between I0A and I1A  $\ge$  2.5  $\mu$ m

- 3.8 Layers CUT, and T1:

- Spacing between <u>CUT</u> and T1 is  $\geq$  19 µm.

- 3.9 Layers M2, and I1A:

- Radius of octagonal area in M2 for JJs is 2.5 µm larger than the radius of window in isolation layer I1A.

#### 4. Overlap and crossing of edges between different layers

#### 4.1 Vias:

- Overlap distance for metallization to largest window in isolation/anodisation is 2.5 µm.

- Via from M0 to M2 must include M1.

#### 4.2 Layer T1:

• Crossing of any structure by T1 is not allowed.

#### 4.3 Layer R1:

- It is only possible to connect R1 by M2 using holes in I2. Other crossings of any structure by R1 are not allowed.

- Distance to next edges below has to be  $\geq$  2.5 µm.

#### 4.4 Layers R1 and I2:

- Outside the connection with M2 the R1 has to be covered by I2.

- 4.5 Layers R1 and M2:

- In the contact hole of layer I2 the resistor has to be covered completely by M2. Overlap of M2 and R1 in the windows of I2 has to be 2.5 µm for shunting resistors and 5 µm for the bias current resistors.

- Crossings of R1 and M2 should be avoided as far as possible.

We offer Design Rules Check (DRC) for customers. The layouts will be checked before starting photo mask preparation.

#### 5. Chip placement on wafer

The standard chip pitch is 5.0 mm x 5.0 mm, The 50 micron width dicing frame decrease the chip size from  $5.0 \times 5.0 \text{ mm}^2$  to a usable area of  $4.9 \times 4.9 \text{ mm}^2$ . For anodisation each chip has to be connected to a 100 µm wide wire between the chips. This has to be done in layer M0.

For projection lithography we use a projection field of 15mm x 15mm. One lithography mask includes 9 chips in standard size. One 4 inch wafer can contain projection fields from different mask sets.

If customers would like to realize their own chip dimensions, please send a request. If wanted, customers can use library cells (JJs of different dimensions, shunted JJs, sections of Josephson Transmission Lines, chip outline, pads ...).

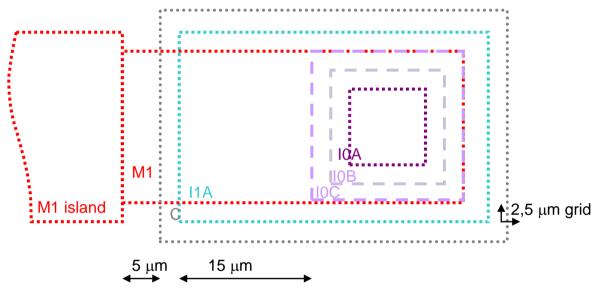

#### 6. Anodisation and cutting

Anodisation of the surface of Niobium is necessary for a good isolation between the metal layers. Therefore all structures in M0 have to be connected to the 50  $\mu$ m wide wire around the chip. If this is not guaranteed by layout, this has to be done with additional wires. Later these additional wires have to be removed. The same has to be done for M1. In M1 it is also possible to make connections to M0. The additional wires for anodisation are removed by the cutting process step. To cut wires it is necessary to put a window for anodisation and isolation below the cut frame.

- For removing a bridge in M1 you have to put windows in I1A and CUT.

- For removing a bridge in M0 you have to put windows in I0A, I0B, I0C, I1A and CUT.

The overlap of M0 or M1 and CUT must be more than 15  $\mu$ m. The length of metal path between design structure and CUT window edge must be more than 5  $\mu$ m. For anodisation M1 islands we recommend following structure.

Recommended design of a cut able contact structure for anodisation of M1

#### 7. Requirements for GDS II file correctness

- GDS II files must be in BLOCK FORMAT, i.e. in size portions of 512 bytes (mostly by default),

- For POLYGONS (GDS II: BOUNDARIES) you cannot use non-orientable self-intersecting polygons. Only orientable self-intersecting polygons (also called re-entrant boundaries) are allowed,

- DATATYPES are ignored,

- Zero width PATHS and TEXT can be used for documentation in layer TEXT,

- For physical text on the mask/wafer we recommend to use real structures as POLYGONS or PATHS. The import of GDS II TEXT can create unforeseeable structures and positions.

- Use only PATHTYPE 0 (normal) or 2 (extended), not PATHTYPE 1 (rounded),

- USER UNIT = 1x10E-6,

- RESOLUTION = 0.001 user unit.

## D. Technology description:

#### 1. Josephson junctions parameters

|                              | Nominal value          | Intra wafer<br>tolerance | On wafer<br>homogeneity | On chip<br>homogeneity |

|------------------------------|------------------------|--------------------------|-------------------------|------------------------|

| Josephson current density    | 1000 A/cm <sup>2</sup> | ± 20 %                   | ± 15 %                  | $\leq$ ± 5 %           |

| Sheet resistance of Mo-layer | 1.0 Ω                  | ± 20 %                   | ± 10 %                  | $\leq$ ± 5 %           |

#### 2. Stripline inductance

| Layer             | L <sub>square</sub> | Intra wafer<br>tolerance | On wafer<br>homogeneity | On chip<br>homogeneity |

|-------------------|---------------------|--------------------------|-------------------------|------------------------|

| M1-M0             | 0.52 pH             | ± 10 %                   | ±5%                     | $\leq$ ± 2 %           |

| M2-M1 (across M0) | 0.64 pH             | ± 10 %                   | ±5%                     | $\leq$ ± 2 %           |

| M2-M0             | 0.81 pH             | ± 10 %                   | ±6%                     | $\leq$ ± 2 %           |

#### **Remarks:**

- Inductances were measured in interferometers with micro strips of 100  $\mu m$  length and 10  $\mu m$  width.

- London penetration depth for magnetic field: (87 ± 5) nm.

- **Capacitance:** Measured value of specific capacitance (defined from Fiske steps; measurements at JJs with w = 10  $\mu$ m l = 30  $\mu$ m and 100  $\mu$ m) is (0.05 ± 0.002) pF/ $\mu$ m<sup>2</sup>.

#### 3. Nominal values of area, critical current, diameter, and shunt resistor for JJs

| A/µm²              | 12.5  | 17.7   | 20.6   | 23.8 | 30.8   | 36.7  | 59.9   |

|--------------------|-------|--------|--------|------|--------|-------|--------|

| l₀/units           | 1.00  | 1.50   | 1.75   | 2.00 | 2.50   | 3.00  | 5.00   |

| l₀/µA              | 125   | 187.50 | 218.75 | 250  | 312.50 | 375   | 625.00 |

| Ø/µm               | 3.8   | 4.6    | 5.0    | 5.4  | 6.1    | 6.7   | 8.5    |

| C <sub>J</sub> /pF | 0.625 | 0.885  | 1.03   | 1.19 | 1.54   | 1.835 | 3.0    |

| R₅/Ω*              | 2.10  | 1.40   | 1.20   | 1.05 | .85    | .70   | .40    |

#### Ø = 2r

#### Remarks:

\*The R<sub>s</sub> value is calculated for adjusting  $\beta_c=1$ .

- JJs areas are realized as octagons.

- Measured ratios of critical currents are correct within ± 5 %.

- The nominal  $I_c R_n$  value is about 256 $\mu$ V.

#### E. Multi custom wafer rules:

To reduce costs we recommend placing designs of some customers together on one wafer. For decreasing the time of placement and better matching conditions:

- Send flat hierarchy designs including only the top cell

- Use chip size of 4.9mm x 4.9mm or 5mm x 5mm including slicing frame

- Set the origin [point 0, 0] to chip center and follow gds2 design rule [rule 7]

### F. Future plans for improvement of the Niobium process:

At this time the development of our technology is still in progress.

# G. Note:

Violation of the design rules may be permitted in special cases, e.g. for connections between trilayer and wiring.

# H. Release Notes:

Version 1.1, Date 24.8.2005:

- 3.8 Layers CUT, and T1:

- Spacing between <u>CUT</u> and T1 is  $\geq$  19 µm.

- 3.9 Layers M2, and I1A:

- Radius of octagonal area in M2 for JJs is 2.5 µm larger than the radius of window in isolation layer I1A.

Version 1.2, Date 22.06.2007:

- A. Photomaske: Column "Wafer resist"

- 2.3 Layer IOA, IOB, I1A, I1B, I2:

- Spacing Inside I0A,  $I1A \ge 2.5 \ \mu m$

Version 1.3, Date 08.06.2011:

Overall: Text edit

- A. Photomask:

- I0A is for anodization and 100nm of SiO insulation

- I0B is only 100nm of SiO insulation

- Process type (etch, anod or liftoff) added

- B. Auxiliary Layers:

- Now SMC add to layer C-I0B and I-I1B

- 2. Width and spacing inside single layers

- Rules for Layer SMA, SMA and M0N

- 5. Chip Placement

- Standard chip size is now 5mm x 5mm

- 7. Requirements for GDS II file correctness

- Avoid GSD II TEXT for physical layers

- E. Multi custom wafer rules:

- Only 5mm x 5mm chips as standard

- Cell origin [point 0, 0] to chip center

Appendix 2 (cross secion)

- I0A for anodisation and 100 nm SiO insulation

- I0B only 100 nm SiO insulation

Appendix 3 (12.8mm standard chip layout): removed

Version 1.4

- Add the layers IOC and I3, edited the whole document for these changes

- Usable chip size is 4.9mm x 4.9 mm, because the 50 micron width dicing frame

- SMC only in I3

#### Version 1.5

• Replace Si0 by SiO<sub>2</sub>, therefore the mask polarity and wafer process has been changed

Version 1.6

• Replacement the contact lithography by projection lithography by implementation of an 5:1 stepper tool

## I. Appendix:

#### 1. Contents of the FLUXONICS Foundry layout library

- Josephson Junctions, shunted and unshunted,

- Pads,

- Chip outline,

- Vias,

- Resistors,

- dc/SFQ & SFQ/dc (dc to Single Flux Quantum & Single Flux Quantum to dc) converters.

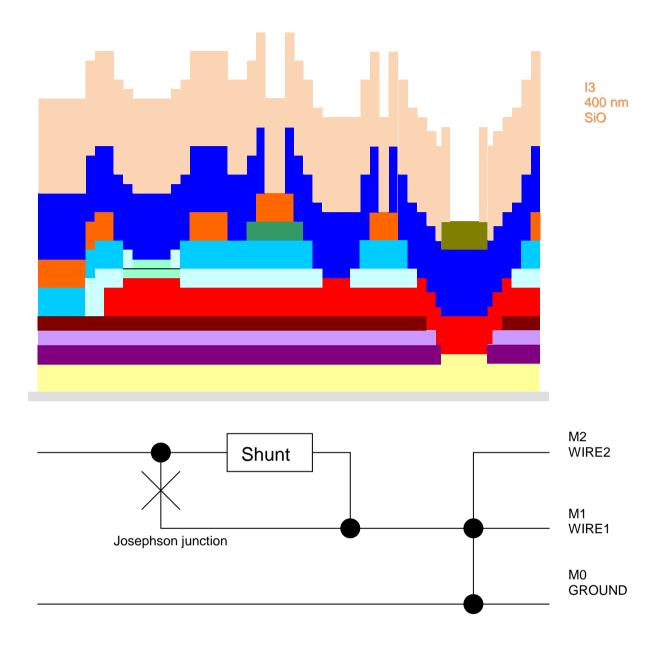

#### 2. Cross section of RSFQ sandwich for the process RSFQ1H

10/12